Uživatelské nástroje

pitel:inp:proj02

Caesarova šifra

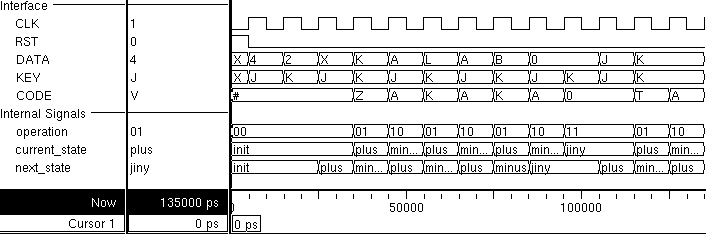

| zpráva: | 4 | 2 | X | K | A | L | A | B | 0 | 0 | J | K |

|---|---|---|---|---|---|---|---|---|---|---|---|---|

| klíč: | J | K | +J | −K | +J | −K | +J | −K | J | K | +J | −K |

| zašif.: | # | # | Z | A | K | A | K | A | 0 | 0 | T | A |

Časový diagram simulace

Grafová reprezentace

caesar.vhdl

library IEEE; use IEEE.std_logic_1164.all; use IEEE.std_logic_unsigned.all; -- Caesar component --------------------------------------------------- entity caesar is port( DATA : in std_logic_vector(7 downto 0); KEY : in std_logic_vector(7 downto 0); CLK : in std_logic; RST : in std_logic; CODE : out std_logic_vector(7 downto 0) ); end caesar; architecture behavioral of caesar is -- internal signals signal operation : std_logic_vector(1 downto 0); signal d_data, d_key: std_logic_vector(7 downto 0); type t_stav is (INIT, PLUS, MINUS, JINY); signal current_state, next_state: t_stav; begin data_reg: process(CLK, RST) begin if (RST = '1') then d_data <= (others => '0'); elsif (CLK'event and CLK = '1') then d_data <= DATA; end if; end process; key_reg: process(CLK, RST) begin if (RST = '1') then d_key <= (others => '0'); elsif (CLK'event and CLK = '1') then d_key <= KEY; end if; end process; sync_logic: process(CLK, RST) --RST begin if (RST = '1') then current_state <= INIT; elsif (CLK'event AND CLK = '1') then current_state <= next_state; end if; end process sync_logic; next_state_logic: process(current_state, DATA) --FSM begin case (current_state) is when INIT => if (DATA >= "01000001" AND DATA <= "01011010") then --AZ next_state <= PLUS; else next_state <= INIT; end if; when PLUS => if (DATA >= "01000001" AND DATA <= "01011010") then --AZ next_state <= MINUS; else next_state <= jiny; end if; when MINUS => if (DATA >= "01000001" AND DATA <= "01011010") then --AZ next_state <= PLUS; else next_state <= jiny; end if; when jiny => if (DATA >= "01000001" AND DATA <= "01011010") then --AZ next_state <= PLUS; else next_state <= jiny; end if; end case; end process next_state_logic; vystup_logic: process(current_state, KEY) --vystupy begin case (current_state) is when INIT => operation <= "00"; when PLUS => operation <= "01"; when MINUS => operation <= "10"; when jiny => operation <= "11"; end case; end process vystup_logic; ALU: process(d_data, d_key, operation) variable temp: std_logic_vector(7 downto 0); begin case (operation) is when "00" => --init code <= "00100011"; --# when "01" => --plus temp := d_data + (d_key - "01000000"); --@ (A-1) if (temp > "01011010") then --Z temp := "01011010"; --Z end if; code <= temp; when "10" => --minus temp := d_data - (d_key - "01000000"); --@ (A-1) if (temp < "01000001") then --A temp := "01000001"; --A end if; code <= temp; when "11" => --jiny code <= d_data; when others => null; end case; end process; end behavioral;

caesar_tb.vhdl

library IEEE; use IEEE.std_logic_1164.all; use IEEE.std_logic_unsigned.all; entity caesar_tb is end caesar_tb; architecture behavioral of caesar_tb is constant period : time := 10 ns; component caesar port( DATA : in std_logic_vector(7 downto 0); KEY : in std_logic_vector(7 downto 0); CLK : in std_logic; RST : in std_logic; CODE : out std_logic_vector(7 downto 0) ); end component; -- Testbench internal signals signal clk : std_logic := '0'; signal rst : std_logic := '1'; signal data : std_logic_vector(7 downto 0); signal key : std_logic_vector(7 downto 0); signal code : std_logic_vector(7 downto 0); begin uut : caesar port map( DATA => data, KEY => key, CLK => clk, RST => rst, CODE => code ); clk <= NOT clk AFTER period / 2; test : process begin wait until clk'event AND clk = '1'; rst <= '0'; key <= "01001010"; --J data <= "00110100"; --4 wait until clk'event AND clk = '1'; key <= "01001011"; --K data <= "00110010"; --2 wait until clk'event AND clk = '1'; key <= "01001010"; --J data <= "01011000"; --X wait until clk'event AND clk = '1'; key <= "01001011"; --K data <= "01001011"; --K wait until clk'event AND clk = '1'; key <= "01001010"; --J data <= "01000001"; --A wait until clk'event AND clk = '1'; key <= "01001011"; --K data <= "01001100"; --L wait until clk'event AND clk = '1'; key <= "01001010"; --J data <= "01000001"; --A wait until clk'event AND clk = '1'; key <= "01001011"; --K data <= "01000010"; --B wait until clk'event AND clk = '1'; key <= "01001010"; --J data <= "00110000"; --0 wait until clk'event AND clk = '1'; key <= "01001011"; --K data <= "00110000"; --0 wait until clk'event AND clk = '1'; key <= "01001010"; --J data <= "01001010"; --J wait until clk'event AND clk = '1'; key <= "01001011"; --K data <= "01001011"; --K wait until clk'event AND clk = '1'; end process; end behavioral;

/var/www/wiki/data/pages/pitel/inp/proj02.txt · Poslední úprava: autor: 127.0.0.1